隨著便攜式電子設備和物聯網的快速發展,低壓系統模擬集成電路(Analog IC)設計已成為半導體行業的重要研究方向。低壓系統通常指工作電壓低于1.8V的電路環境,其設計在功耗、集成度和性能方面面臨獨特挑戰,同時也催生了眾多創新解決方案。

一、低壓模擬IC設計的核心挑戰

低壓環境下,模擬集成電路設計需克服多重技術難點:電源電壓降低導致信號動態范圍壓縮,增加了噪聲和失真的影響;晶體管閾值電壓未同比降低,使得過驅動電壓受限,電路增益和線性度下降;工藝波動和溫度變化對低壓電路的影響更為顯著,設計要求更高的魯棒性。

二、關鍵技術與發展趨勢

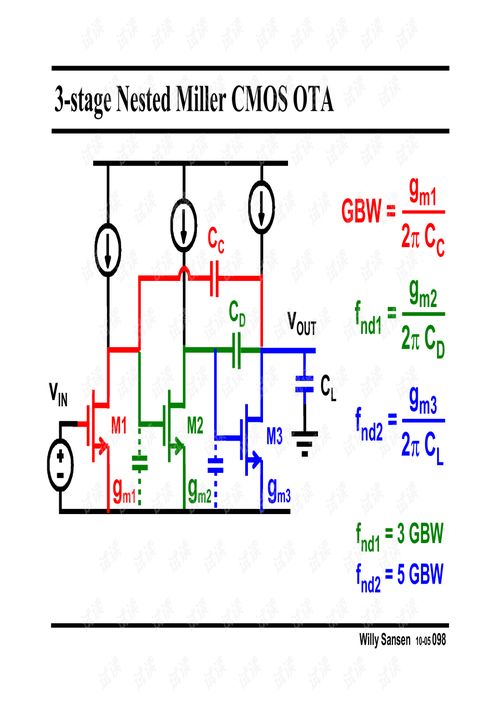

為應對上述挑戰,低壓模擬IC設計采用了多種先進技術:

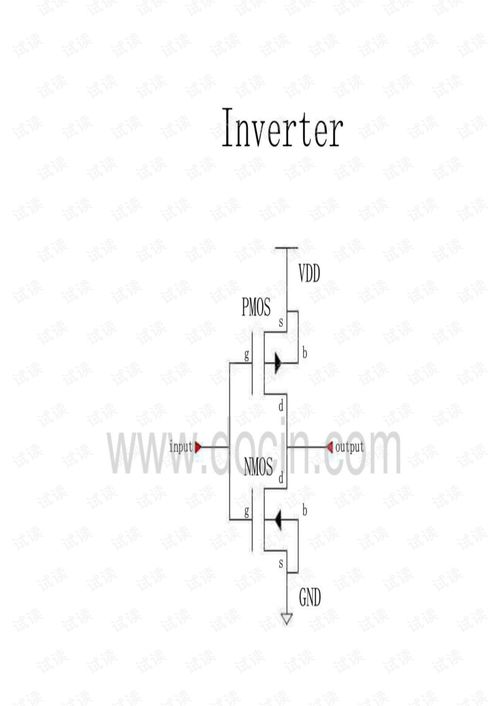

- 亞閾值設計:利用MOSFET在亞閾值區的工作特性,顯著降低功耗,適用于生物醫療傳感器等超低功耗場景。

- 開關電容技術:通過電荷轉移實現信號處理,降低對絕對電壓精度的依賴,廣泛應用于ADC和濾波器設計。

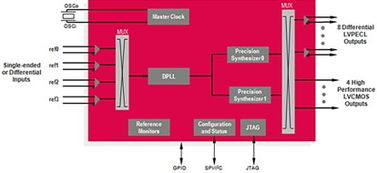

- 自適應偏置與校準:集成數字輔助電路,實時補償工藝、電壓和溫度(PVT)變化,提升性能一致性。

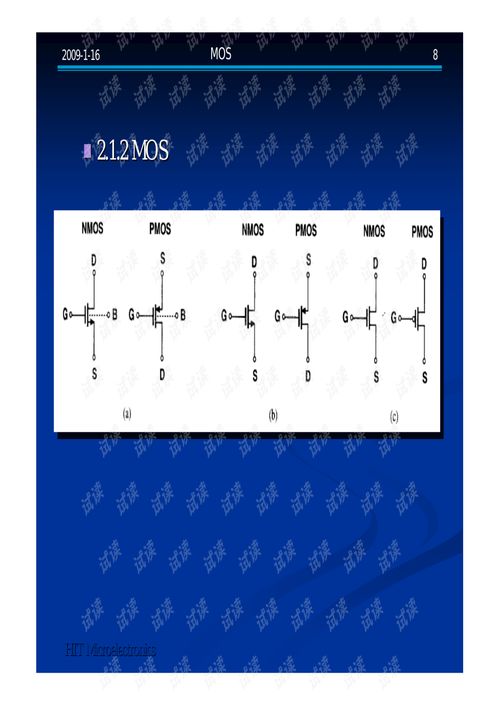

- 新型器件與架構:如FinFET和FD-SOI技術的引入,改善了低壓下的匹配特性與泄漏控制。

三、典型應用領域

低壓模擬IC已深入多個關鍵領域:

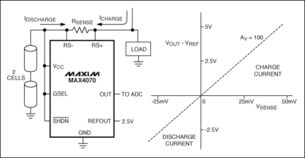

- 可穿戴設備:心電監測、運動傳感器等需長續航的設備,依賴低壓運算放大器和數據轉換器。

- 能量收集系統:從環境采集微弱能量(如太陽能、熱能),需高效電源管理芯片與超低壓啟動電路。

- 物聯網節點:無線傳感網絡中的模擬前端(AFE)電路,要求在毫瓦級功耗下實現高精度信號調理。

四、未來展望

隨著5G通信、人工智能邊緣計算的需求增長,低壓模擬IC設計將進一步向高能效、高集成度方向發展。技術融合(如模擬-數字混合設計)和材料創新(如二維半導體)有望突破現有電壓限制,為下一代電子系統奠定基礎。同時,設計自動化工具與仿真方法的進步,將加速低壓模擬IC在更廣泛領域的應用落地。

低壓系統模擬集成電路設計雖充滿挑戰,但通過技術創新與跨學科協作,正持續推動電子設備向更節能、更智能的方向演進。